## 2025 IEEE VLSI Review

고려대학교 전기전자공학부 석사과정 심승우

이번 2025 IEEE VLSI Symposium에서는 Wireless 관련 두 개의 세션이 열렸으며, 각 세션 당 네 편의 논문이 소개되었다. 이 중 본 리뷰에서는 Session 2에서는 Ka-band 대역의 Receiver와 PA, 그리고 Session 28에서는 D-band Transceiver 논문까지 총 세 편을 다룬다.

### Session 2 RF/mm-wave Tx and Rx

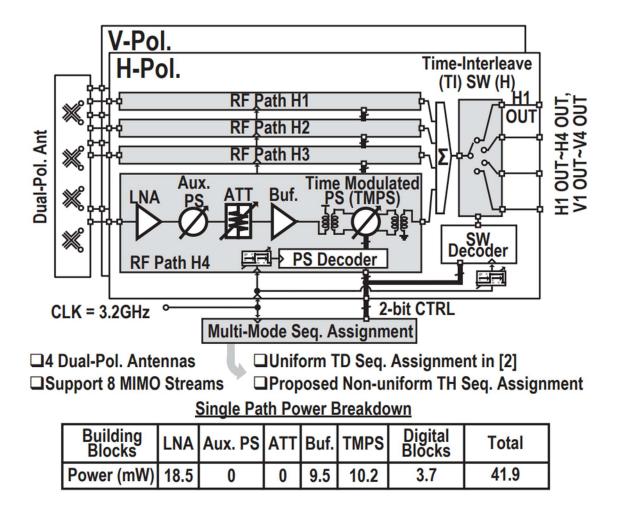

#2-1 이번에 리뷰할 논문은 도쿄공업대학의 Kenichi Okada 교수님 그룹에서 발표한 "A Ka-Band 8-Stream Phased-Array Receiver with Time-Hopping Blocker Rejection for 6G Applications"이다. 차세대 6G 통신에서는 데이터 전송량 증가를 위해 다중 안테나 기반 의 MIMO(Multiple-Input Multiple-Output) 기술이 필수적이다. 주파수가 높아질수록 안테 나 소형화가 가능해 다수의 안테나를 집적할 수 있지만, 기존 방식은 빔과 스트림을 1:1 로 매칭해야 하므로 칩 면적과 전력 소모가 크다는 한계가 있었다. 이를 개선하기 위해 시간 분할(Time-Division, TD) 기법이 도입되었으나, 나이퀴스트율(Nyquist-rate)로 빠르게 스트림을 스위칭하는 과정에서 블로커(Blocker) 신호의 앨리어싱(aliasing) 문제가 발생하 며, 이를 억제하기 위해서는 별도의 anti-aliasing 필터가 필요했다. 본 논문은 비균일 (Non-uniform) 타임호핑(Time-Hopping, TH) 기법을 활용하여 이러한 문제를 해결한 것이 핵심이다. 기존 TD 기법이 고정된 순서로 스트림을 스위칭하는 반면, 제안된 기법은 N 주기마다 스트림을 무작위 순서로 전환한다. 이를 통해 블로커 신호의 스펙트럼을 분산. 재형성(reshaping)하여, 필터 없이도 블로커 앨리어싱을 억제할 수 있음을 보였다. 이는 ADC 및 서브샘플링 수신기에서 널리 사용되는 비균일 샘플링 기법에서 착안한 것이다. 구현된 칩은 65nm CMOS 공정 기반으로 제작되었으며, 8개의 RF 경로와 8-way 타임인 터리브 스위치로 구성된다. 듀얼 폴라라이제이션 안테나(H-Pol., V-Pol.)와 결합해 총 8개 스트림을 수신할 수 있다. 측정 결과, 64QAM OFDM 변조에서 38.4Gbps의 데이터 전송률 을 -23.5 dB EVMRMS와 함께 달성하였다. 또한, 제안된 비균일 TH 모드에서는 기존 균일 TD 모드 대비 최대 34 dB 높은 블로커 허용도(Blocker Tolerance)와 42.9 dB의 블로커 앨 리어싱 억제 성능을 보였다. 결론적으로, 본 연구는 스트림당 최소 RF 경로 수로 최고 데이터 전송률을 기록하면서도, 블로커 앨리어싱 문제를 효과적으로 해결했다는 점에서 의의가 크다. 향후 6G 초고속 무선 통신 시스템에서 고효율·저면적 위상 배열 수신기의 가능성을 제시한 연구라 할 수 있다.

[그림1] "2.1 A Ka-Band 8-Stream Phased-Array Receiver with Time-Hopping Blocker Rejection for 6G Applications " 구조

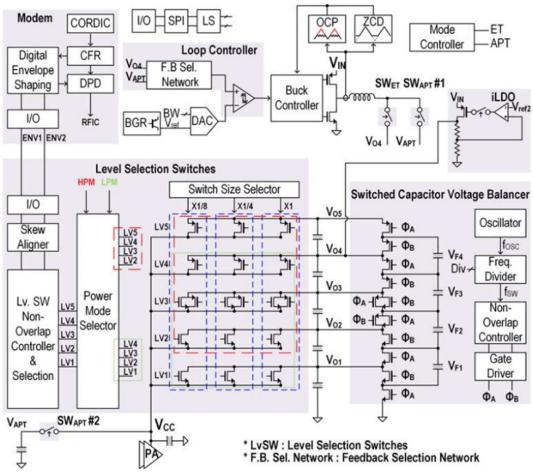

#2-4 이번 논문은 부산대학교 백지선 교수님 그룹에서에서 발표한 "A Digital Envelope Tracking RF Power Amplifier Achieving 400MHz Channel Bandwidth and 91.9% Efficiency for Upper-Mid Band Extreme Massive MIMO 6G Communications"이다. 6G 이동통신에서 주목받는 7~24GHz FR3 대역은 높은 PAPR을 갖는 OFDM 신호 특성 때문에 전력증폭기의 효율 저하가 심각하다. 모바일 단말기의 경우 출력 전력이 1W 미만으로 줄어들고 있지만, 여전히 선형성과 효율을 동시에 확보하기 어려운 상황이다. 이를 해결하기 위해 디지털 엔벌로프 트래킹(digital envelope tracking, DET) 기반의 새로운 공급 변조 기법을 제안하였다. 제안된 구조는 시리즈 스위치 기반 DET 방식으로, 레벨 선택 스위치와 셀 슬라이싱(cell slicing)을 통해 전압을 세밀하게 제어하면서 효율을 높인다. 또한, 내부 LDO를 추가해 모드 전환 시 발생하는 전압 불안정 문제를 억제하여 안정적인 동작을 보장한다. 측정에서는 130nm BCD 공정을 기반으로 제작된 DET IC를 13GHz 대역 GaN PA와 결합해 동작을 검증하였다. 이 PA의 포화 출력은 25 dBm이며, 출력 17 dBm에서 최대 효율

91.9%를 달성하였다. 특히 동일 출력에서 고정 전압 PA 대비 100 mW 이상의 전력 절감 효과를 보였다. 또한 400 MHz 64QAM 신호에서도 2.81%의 EVM과 -36.8 dBc의 ACLR을 기록하여, 초광대역에서도 선형성과 효율을 동시에 충족함을 입증하였다. 결론적으로, 이연구는 모바일 단말기용 PA에서 DET 기술을 적용해 고효율·저전력 동작을 실현했으며,특히 17 dBm 동작점에서 효율과 전력 절감 효과를 동시에 보여준 것이 핵심적인 성과이다. 이는 6G FR3 대역의 모바일 기기 송신단 설계에서 중요한 의미를 갖는다.

[그림1] "2.4 A Digital Envelope Tracking RF Power Amplifier Achieving 400MHz Channel Bandwidth and 91.9% Efficiency for Upper-Mid Band Extreme Massive MIMO 6G

Communications " 구조

#### **Session 28 Sub-THz TRXs**

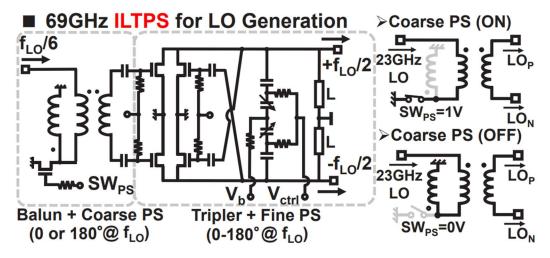

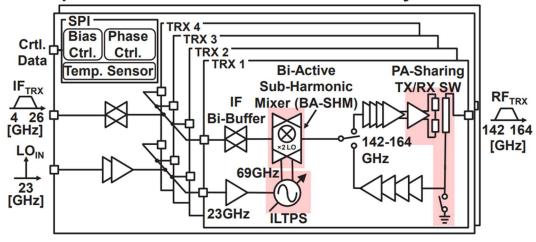

#28-1 이번에 리뷰할 논문은 도쿄공업대학 Kenichi Okada 교수님 그룹에서 발표 한 "A 150 GHz High-Power-Density Phased-Array Transceiver in 65nm CMOS for 6G UE Module"이다. 차세대 6G 무선통신에서는 100 Gbps를 넘는 초고속 데이터 전송을 위해 서브-THz 대역, 특히 140GHz 부근의 D-band가 중요한 후보로 떠오 르고 있다. 그러나 지금까지 발표된 대부분의 D-band 트랜시버는 대형 칩과 안 테나 모듈을 사용하는 기지국(base station)이나 백홀(backhaul) 용도로만 설계되 어 왔다. 본 연구는 이와 달리, 세계 최초로 사용자 단말기(UE)를 위한 D-band 안테나-인-패키지(AiP) 모듈 기반 트랜시버를 제시했다는 점에서 의의가 있다. 이 연구의 핵심은 LO 체인의 면적과 전력 소모 문제를 해결하기 위해 제안된 injection-locked tripling phase shifter (ILTPS)이다. 기존의 heterodyne LO 체인은 믹서의 충분한 변환 이득을 위해 다단 곱셈기와 버퍼를 사용해야 하므로 면적과 소비전력이 크다는 단점이 있었다. 이에 비해 ILTPS는 23 GHz 입력을 받아 69 GHz 신호로 3배수 변환하면서 동시에 위상 천이 기능을 수행한다. Varactor 전압 을 조절해 LC 공진 주파수를 변화시키면 -45°에서 +45°까지 정밀한 위상 제어가 가능하고, 추가적으로 입력 측 밸런을 통해 약 30°의 위상 조정이 이루어진다. 이 후 3배와 2배의 주파수 곱셈 과정을 거쳐 최종적으로 360° 위상 제어를 실현할 수 있다. ILTPS는 LO 버퍼를 생략하고 믹서에 직접 연결함으로써 큰 전압 스윙을 확보할 수 있으며, injection locking 메커니즘을 통해 안정적인 주파수 동작을 보 장한다. 그 결과 기존 LO 체인 대비 면적과 전력 소모를 크게 줄이면서도 낮은 RMS 위상·이득 오차를 달성하였다. 또한, 본 트랜시버의 PA/LNA 프런트엔드와 안테나 스위치는 다음과 같이 설계되었다. 기존 안테나 스위치는 shunt 트랜지스 터의 기생 커패시턴스로 인해 송신·수신 경로 손실 사이의 트레이드오프가 발생 하는 문제가 있었다. 이를 해결하기 위해, 안테나 스위치는 PA와 LNA의 매칭 네 트워크에 통합되었으며, 송신 경로에는 별도의 스위칭 소자가 존재하지 않는다. 또한 shunt 스위치의 기생 커패시턴스는 입력 밸런 인덕턴스에 의해 상쇄된다. PA/LNA 자체는 여러 증폭 단으로 구성되어 있고, feedback gm-boosting 기법을 적용해 이득과 선형성을 확보하였다. 측정 결과, 제안된 150 GHz 트랜시버는 65nm CMOS 공정으로 제작되었으며 8-소자 AiP 모듈 형태로 구현되었다. 동작 주파수 범위는 142-164 GHz로, 최대 EIRP는 25.7 dBm을 기록하였다. 단일 소자 기준 소비전력은 송신 모드에서 150 mW, 수신 모드에서 93 mW이며, 이는 종래연구 대비 소모 전력이 가장 낮은 수준이다. 전송 실험에서는 0.3 m 거리에서 송신 시 최대 56 Gbps, 수신 시 40 Gbps의 데이터율을 달성했으며, 5 m 거리에서도 QPSK 변조로 20 Gbps를 유지하였다. 위상 제어 시 RMS 이득 오차는 0.18 dB, 위상 오차는 0.79°로 측정되어 매우 정밀한 범포밍 성능을 보였다. 결론적으로, 본논문은 D-band 주파수 대역에서 세계 최초로 사용자 단말기용 AiP 기반 트랜시버를 제시하고, 단위 면적당 최고 EIRP와 최저 전력 소모를 동시에 달성한 연구이다. 이는 6G UE 모듈의 실현 가능성을 보여주는 중요한 이정표로 평가된다.

# ☐ Proposed 150GHz 8-Element Phased-Array Transceiver

[그림1] "28.1 A 150 GHz High-Power-Density Phased-Array Transceiver in 65nm CMOS for 6G UE Module " 구조

# 저자정보

## 심승우 석사과정 대학원생

◆ 소속 : 고려대학교 전기전자공학과◆ 연구분야 : mm-Wave IC design

• 이메일 : lisang@korea.ac.kr

● 홈페이지 : https://arfsl.korea.ac.kr